Introduction to tinyAVR Microcontroller Attiny404 Architecture, Features, and Related Registers with a Simple Code Example

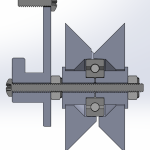

In this continuation of the tinyAVR tutorial series, this blog post delves into the AVR CPU architecture, capabilities, and registers. Table of Contents Features Overview AVR is a well known 8-bit CPU. The CPU is a heart of the device which can access memories, do calculations, execute instructions, control peripherals as well handle interrupt routines. Most part of this post is based on the official Attiny404 documentation, so for in-depth info check the datasheet. Architecture AVR CPU uses a Harvard architecture with separate buses for program and data. While one instruction is being executed by the CPU, the second is being fetched from the program memory – this pipeline allows instructions to be executed on each clock cycle. As you can see in the image above, the CPU has ALU – Arithmetic Logic Unit. It can do logic and/or arithmetic operations between two registers or a constant value and a register. Also, ALU can execute single-register operations. When the ALU finishes an arithmetic operation, the STATUS register gets updated with the information about the operation end result. The ALU can directly access to a register file which consists of 32 8-bit general purpose working registers. All these registers have single clock cycle access time. To sum up, this allows single cycle arithmetic operations between two registers. Memory overview The program memory bus is directly connected to Flash, the addresses start from 0x0000. Whole data memory space is…